目前我见到的所有芯片中都含有 PLL 模块,而且一直不知道如何利用 PLL 对晶振进行倍频的,这次利用维基百科好好的学习了下 PLL 的原理。

1. 时钟与振荡电路

在芯片中,最重要的就是时钟,时钟就像是心脏的脉冲,如果心脏停止了跳动,那人也就死亡了,对于芯片也一样。了解了时钟的重要性,那时钟是怎么来的呢?时钟可以看成周期性的0与1信号变化,而这种周期性的变化可以看成振荡。因此,振荡电路成为了时钟的来源。

振荡电路的形成可以分两类:

- 石英晶体的压电效应:电导致晶片的机械变形,而晶片两侧施加机械压力又会产生电,形成振荡。它的谐振频率与晶片的切割方式、几何形状、尺寸有关,可以做得精确,因此其振荡电路可以获得很高的频率稳定度。

- 电容 Capacity 的充电放电:能够存储电能,而充放电的电流方向是反的,形成振荡。可通过电压等控制振荡电路的频率。

2. PLL与倍频

由上面可以知道,晶振由于其频率的稳定性,一般作为系统的外部时钟源。但是晶振的频率虽然稳定,但是频率无法做到很高(成本与工艺限制),因此芯片中高频时钟就需要一种叫做压控振荡器(Voltage Controlled Oscillator)的东西生成了(顾名思义,VCO 就是根据电压来调整输出频率的不同)。可压控振荡器也有问题,其频率不够稳定,而且变化时很难快速稳定频率。哇偶,看到这种现象是不是很熟悉?嘿嘿,这就是标准开环系统所出现的问题,解决办法就是接入反馈,使开环系统变成闭环系统,并且加入稳定的基准信号,与反馈比较,以便生成正确的控制。

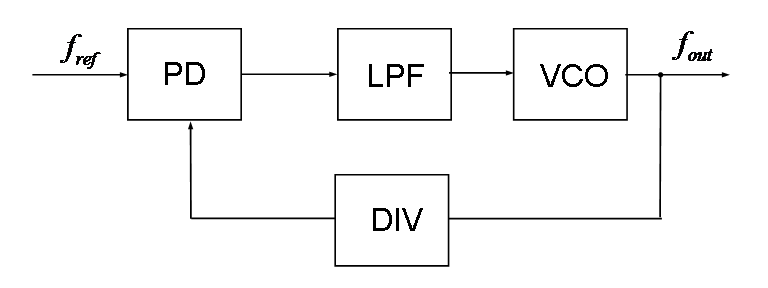

因此,为了将频率锁定在一个固定的期望值,锁相环PLL出现了!一个锁相环PLL电路通常由以下模块组成:

- 鉴相鉴频器 PFD(Phase Frequency Detector):对输入的基准信号(来自频率稳定的晶振)和反馈回路的信号进行频率的比较,输出一个代表两者差异的信号

- 低通滤波器 LPF(Low-Pass Filter):将PFD中生成的差异信号的高频成分滤除,保留直流部分

- 压控振荡器 VCO(Voltage Controlled Oscillator):根据输入电压,输出对应频率的周期信号。利用变容二极管(偏置电压的变化会改变耗尽层的厚度,从而影响电容大小)与电感构成的 LC 谐振电路构成,提高变容二极管的逆向偏压,二极管内耗尽层变大,电容变小,LC 电路的谐振频率提高,反之,降低逆向偏压时,二极管内电容变大,频率降低

- 反馈回路FL(Feedback Loop):通常由一个分频器实现。将 VCO 的输出降低到与基准信号相同级别的频率才能在 PFD 中比较

PLL 工作的基本原理就是将压控振荡器的输出经过分频后与基准信号输入 PFD,PFD 通过比较这两个信号的频率差,输出一个代表两者差异的信号,再经过低通滤波器转变成一个直流脉冲电压去控制 VCO 使它的频率改变。这样经过一个很短的时间,VCO 的输出就会稳定下来。所以:

PLL 并不是直接对晶振进行倍频,而是将频率稳定的晶振作为基准信号,与 PLL 内部振荡电路生成的信号分频后进行比较,使 PLL 输出的信号频率稳定

最后,根据原理,理解一下锁相环(Phase Locked Loop)的名称

- 为了对基准信号与反馈信号进行频率比较,二者的相位必须相同且锁住,任何时间都不能改变,这样才能方便的比较频率,所以叫锁相(Phase Locked)

- 为了快速稳定输出系统,整个系统加入反馈成为闭环,所以叫环(Loop)